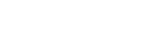

文章图片

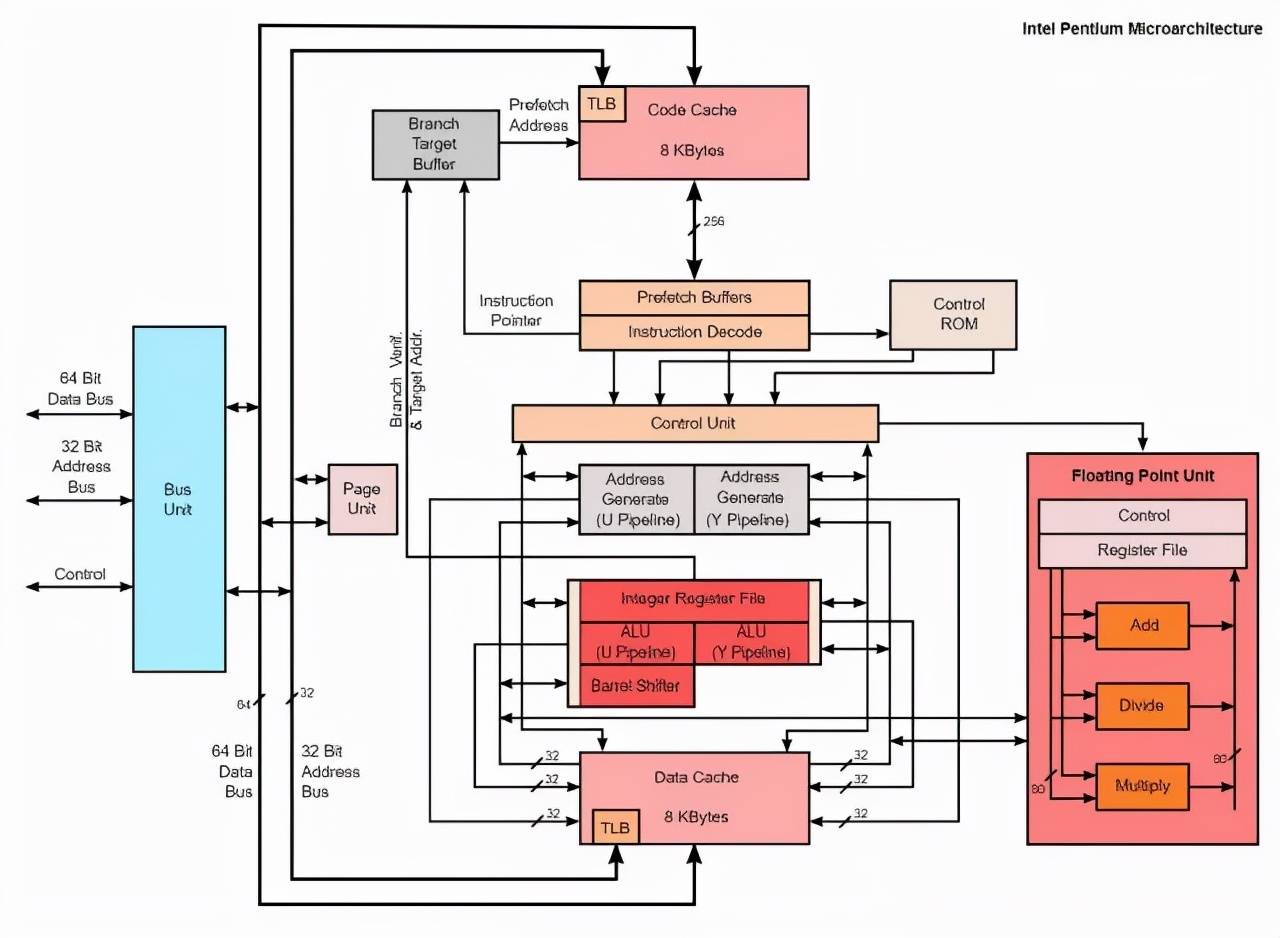

AMD K5 框架图如下图所示:

文章图片

如果你曾经研究过微处理器原理图 , 你可能会发现 K5 和微处理器有许多相似之处 , 但奔腾却相反 。 AMD 在 Nx586 上市后收购了 NexGen 。 K5 是 AMD 自主设计的 , 而 K6 最初是 NexGen 的产品 。 也是从那时开始 , CPU 变得像今天我们熟悉的样子 。 设计这些芯片的工程师曾表示:这些相似之处不仅仅是表面上的 。

早在 1996 年 , AMD 的 David Christie 就在 IEEE Micro 上发表了一篇关于 K5 的文章 , 阐述了 K5 是如何将 RISC 和 CISC 结合在一起的 , 这里引用一段该文章的内容:

我们开发了一个松散地基于 29000 指令集的微型 ISA 。 一些额外的控制字段将微指令的大小扩展到 59 位 。 其中一些简化并加速了超标量控制逻辑 , 其他的用于提供特定于 x86 的功能 , 这些功能对于性能非常重要 , 因此不能用微指令序列来合成 。 但是这些微指令仍然遵循基本的 RISC 原则:简单的寄存器到寄存器操作 , 对寄存器指定符和其他字段进行固定位置编码 , 并且每个操作不多于一个内存引用 。 因此我们称它们为 RISC 操作 , 或简称为 ROPs 。 这种简单、通用的特性为实现更复杂的 x86 操作提供了灵活性 , 从而有利于保持执行逻辑相对简单 。

RISC 微架构最关键的一点是 x86 指令集的复杂性止于解码器 , 并且在很大程度上对乱序执行内核是透明的 。 这种方法只需要很少的额外控制复杂度 , 而不需要乱序的 RISC 执行来实现乱序的 x86 执行 。 任务切换的 ROP 序列看起来并不比简单指令串的 ROP 序列复杂 。 执行内核的复杂性被有效地从架构的复杂性中分离出来 , 而不是复合起来的 。Christie 并没有混淆 ISA 与 CPU 物理实现细节之间的区别 。 他认为物理实现本身在一些重要的方面是 RISC 式的 。 K5 重用了 AMD 为其 Am29000 系列 RISC CPU 开发的执行后端部分 , 它实现了一个比原生 x86 ISA 更类似于 RISC 的内部指令集 。 在此期间 , NexGen 和 AMD 引用的 RISC 式技术参考了数据缓存、pipeline 和超标量架构等参考概念 。

这些想法都不是严格的 RISC , 但它们都是首先在 RISC CPU 中首次亮相的 , 将这些功能作为「类 RISC」进行营销是有道理的 。

这些功能与 RISC 的相关程度以及 x86 CPU 是否解码 RISC 样式指令 , 取决于选择的框架标准 。 这一争论比奔腾 Pro 还大 , 即使 P6 是与乱序执行引擎等技术发展最相关的微架构 。 不同公司的工程师都有自己的看法 。

现代 x86 CPU 的压力

推荐阅读

- 年轻人|呼叫全城玩家,魔都首发「表情包地铁」启程,2022蓝不倒!

- Google|谷歌暂缓2021年12月更新推送 调查Pixel 6遇到的掉线断连问题

- 数字货币|2021年加密货币市场盘点:比特币仍是霸主,NFT进入大众视野

- 文章|美媒文章:古人类领域2021年六大新突破

- 牛上|英媒文章:2021年最有趣的科学发现

- 视点·观察|科技行业都在谈论“元宇宙”,可是它还不存在

- IT|新能源汽车年底卖爆 展车都被抢购 咋回事?

- 技术|科技赋能创新发展

- 植被|二十年后的成都

- 何由|2021年,奔向星辰大海的脚步更稳更远!